УДК 004.61

Informatics and Mathematical Methods in Simulation Vol. 6 (2016), No. 4, pp. 315-321

# ФОРМАЛИЗАЦИЯ ПРЕДСТАВЛЕНИЯ ПОСЛЕДОВАТЕЛЬНОСТИ ТЕСТОВЫХ ГИПОТЕЗ ПРИ ДИАГНОСТИРОВАНИИ ЭЛЕКТРОННЫХ СХЕМ

**А.А.** Верлань<sup>1</sup>, Ю. Стертен<sup>1</sup>, С.А. Положаенко<sup>2</sup>

<sup>1</sup> Норвежский университет науки и технологий, NTNU Gjøvik, Teknologiveien 22, 2815 Gjøvik, Norway; e-mail: andriy.verlan@ntnu.no <sup>2</sup> Одеський національний політехнічний університет, просп. Шевченка, 1, Одеса, 65044, Україна; e-mail: polozhaenko@mail.ru

Разработана процедура формализованного представления последовательности пробных (тестовых) гипотез в ходе проверки исправности электронных устройств при их декомпозиции на подсхемы. Процедура доведена до практического алгоритма, обеспечивающего эффективный (с точки зрения минимизации трудоемкости) поиск неисправных подсхем электронного устройства.

**Ключевые слова:** электронное устройство, подсхема, диагностика, тестовая гипотеза, обучающая последовательность, алгоритм локализации неисправности

#### Введение

В литературе известен [1, 2] и нашел практическое применение [3] при диагностике электронных устройств (ЭУ) метод обучающих проверочных характеристик (ОПХ), который заключается в поочередной проверке гипотез о неисправности подсхем ЭУ.

При этом важным ограничением на проверяемые подсхемы, входящие в состав ЭУ, является количество их полюсных узлов, которое должно быть не больше числа измеряемых сигналов. Так как количество подсхем, полученных в результате разбиения схемы ЭУ на подсхемы, с таким ограничением может быть достаточно велико, то и перебор всех гипотез получается весьма трудоемким. Поэтому целесообразно сформировать последовательность проверки гипотез, позволяющую избежать перебора всех подсхем.

Наиболее естественной является такая последовательность проверки гипотез, при которой сначала проверяются самые большие (в некотором смысле подсхемы). После определения неисправной из них, проверке подвергаются большие, вложенные в предыдущие, и так далее. Т.е. таким образом, достигается направленный поиск неисправной области.

### Цель работы

Целью работы является выполнение формализации процесса получения последовательности тестовых гипотез определения неисправной подсхемы ЭУ и разработка алгоритма ее локализации.

#### Основная часть

Введем понятие размера подсхем и отношения вложенности между ними.

Пусть электрическая схема ЭУ задана с помощью графа G(V,E), где V и E соответственно множества вершин и ребер графа. Тогда подсхеме  $S_i^0$  будет соответствовать подграф  $G_i^0(V_i^0,E_i^0)$ , а остальной части схемы (иначе подсхеме  $S_i^1$ ) —  $G_i^0(V_i^0,E_i^0)$  такие, что

$$V_i^1 \subset V; \ V_i^0 \subset V; V_i^1 \cup V_i^0 = V; V_i^1 \cap V_i^0 = V_i^p,$$

(1)

$$E_i^1 \subset E; \ E_i^0 \subset E; E_i^1 \cup E_i^0 = E; E_i^1 \cap E_i^0 = \phi$$

(2)

где  $V_i^{\ p}$  – множество полюсных узлов подсхемы  $S_i^{\ 0}$  .

Разобьем множество обучающих узлов  $N_{\text{об}}$  на два подмножества:

$$\begin{split} N^0_{\text{o}\delta_i} &\subset \text{V}^0_i\,,\\ N^1_{\text{o}\delta_i} &\subset \text{V}^1_i\,,\\ N^0_{\text{o}\delta_i} &\cup N^1_{\text{o}\delta_i} = N_{\text{o}\delta}. \end{split}$$

Тогда число полюсов подсхемы  $S_i^0$  должно удовлетворять условиям:

$$\operatorname{card} V_i^p - 1 \le \operatorname{card} N_{\text{ofi}}^1, \tag{3}$$

где

$$N_{\text{od}_i}^1 \cap N_{\text{od}_i}^0 = \phi$$

.

Обозначим через  $M^0 = \left\{S_i^0\right\}$  множество всех возможных подсхем проверяемой цепи. Такое множество можно получить, например, рассматривая всевозможные комбинации узлов. Отбирая из  $M^0$  подсхемы, удовлетворяющие (3), мы получим множество M подсхем, которые могут быть проверены при имеющемся наборе доступных узлов

$$M = \{S_i^0 : \operatorname{card} V_i^p - 1 \le \operatorname{card} N_{\operatorname{od}_i}^0\}.$$

Рассмотрим ребро графа  $e = (v_i; v_k)$ . Из (1) и (2) следует, что

если

$$e \in E_i^1$$

, то  $v_j \in V_i^1$ ,  $v_k \in V_i^1$  если  $e \in E_i^0$ , то  $v_j \in V_i^0$ ,  $v_k \in V_i^0$  (4)

Иначе говоря, подсхема  $S_i^1$  при таком ее определении полностью определяется вершинами своего графа, т.е.

если

$$v_i \in V_i^1$$

,  $v_k \in V_i^1$ , то  $y = (v_i, v_k) \in E_i^1$ . (5)

Большинство элементов ЭУ может быть представлено при помощи двухполюсных элементов, соединенных в соответствии с их схемами замещения [4-7]. Однако разбиение схем на подсхемы должно производиться без разбиения схем замещения на составные части, так как физически возможна замена только неисправного элемента целиком.

Для схем ЭУ, содержащих многополюсные элементы, вместо понятия ветвь будем использовать понятие элемент, характеризующийся тем, что он может быть инцидентен более чем двум узлам. Тогда будем считать, что элемент  $q=(\nu_j,...,\nu_k)$  включается в подсхему  $S_i^1$ , если  $\forall \, \nu_j, \nu_k \in V_i^1$ . В противном случае,  $q \in S_i^0$ . Т.е. состав подсхемы  $S_i^1$  в схеме, содержащей многополюсные элементы, тоже будет полностью определяться множеством ее узлов  $V_i^1$ .

Под размером  $\mu_i^1$  подсхемы  $S_i^1$  будем понимать количество ее узлов, т.е.

$$\mu_i^1 = \operatorname{card} V_i^1. \tag{6}$$

Будем говорить, что подсхема  $S_i^1$  больше подсхемы  $S_j^0$  , если

$$\mu_{i}^{1} > \mu_{i}^{0}$$

.

Подсхему  $S_i^0$  будем называть вложенной в подсхему  $S_i^1$ , если

$$V_i^0 \subset V_i^1$$

,

и будем обозначать это как  $S_i^0 \subset S_i^1$ .

Введем понятие о некоторых операциях над подсхемами.

Пусть  $M^* = \left\{S_k^*\right\}$  и  $M^{**} = \left\{S_k^{**}\right\}$  — множества всех вложенных подсхем для двух произвольных проверяемых цепей ( $\forall M^*, M^{**} \subset M$ ).

Объединением подсхем  $S_i^1$  и  $S_j^0$  будем называть подсхему  $S_k^*$ , такую, что

$$V_i^1 \cup V_j^0 = V_k^*,$$

и будем обозначать  $S_k^* = S_i^1 \cup S_j^0$ .

Пересечением подсхем  $S_i^1$  и  $S_j^0$  будем называть подсхему  $S_k^{**}$  , такую, что

$$V_i^1 \cap V_j^0 = V_k^{**},$$

и будем обозначать  $S_k^{**} = S_i^1 \cap S_j^0$ . Очевидно, что

$$S_i^1 \cup S_j^0 \subset M^* \subset M,$$

$S_i^1 \cap S_j^0 \subset M^{**} \subset M.$

Однако эти соотношения не выполняются для множества M, что связано с необходимостью выполнения условия (3) .

Следует отметить, что если  $S_j^0 \subset S_i^1$ , то неисправность  $S_j^0$  влечет за собой и неисправность  $S_i^1$ . Поэтому подсхемы  $S_j^0$  и  $S_i^1$  являются неразличимыми относительно множества обучающих узлов  $N_{\text{об}_i}^1$ . Другими словами, вложенность двух подсхем является достаточным условием их неразличимости. Это позволяет избежать проверки гипотез для группы заведомо неразличимых подсхем. Таким образом, сначала необходимо проверить гипотезы о неисправности максимальных подсхем. Эти подсхемы образуют множество  $M^1 \subset M$  такое, что

$$M^{1} = \{S_{i}^{1} : \forall i \ \overline{\exists} \ S_{k}^{*} \subset M \ S_{i}^{1} \subset S_{k}^{*} \ i \neq k\}, \tag{7}$$

т.е.  $S_i^1$  уже не вложены ни в какие подсхемы из M .

После определения неисправной подсхемы  $S_i^1$  производится проверка гипотез для максимально больших вложенных в нее подсхем, образующих множество  $M_i^1$ :

$$M_i^1 = \{S_j^0 : \forall j \ \overline{\exists} \ S_k^* \subset M_i^1 : S_j^0 \subset S_k^* \ j \neq k\},$$

т.е.  $S_i^0$  уже не вложены ни в какие подсхемы из  $M_i^1$ .

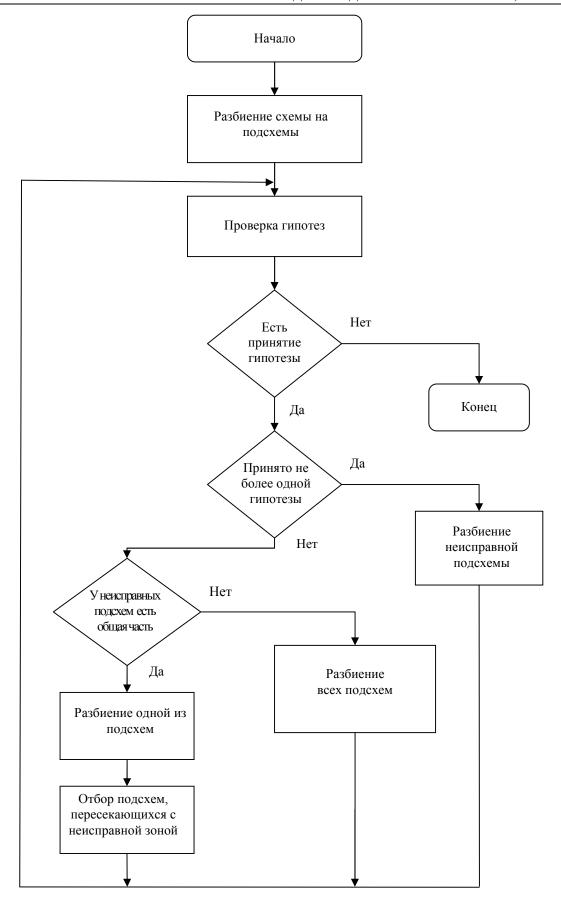

При проверке гипотез на каждом этапе разбиения возможны следующие случаи:

<u>Случай 1</u>. Принимается одна гипотеза. В этом случае производят разбиение неисправной подсхемы на максимально большие подсхемы и осуществляют для них проверку гипотез.

Случай 2. Принимается несколько гипотез о неисправности пересекающихся подсхем, имеющих общую часть, которую и считают зоной неисправности. В этом случае одну из неисправных подсхем разбивают на максимально большие вложенные подсхемы, и гипотезы проверяют для тех подсхем, которые пересекаются с зоной неисправности.

<u>Случай 3</u>. Принимается несколько гипотез о неисправности подсхем, не имеющих одной общей для всех них части. В этом случае производят разбиение всех подсхем, соответствующих принятым гипотезам, а результаты проверяемых гипотез рассматриваются совместно.

<u>Случай 4</u>. Ни одна из рассматриваемых гипотез не принимается. В этом случае процесс локализации заканчивается констатацией неисправности подсхем, полученных на предыдущем шаге разбиения.

Алгоритм локализации неисправности приведен на рис. 1.

Использование численных методов для решения систем уравнений определяет специфику алгоритма принятия решения для каждой гипотезы. В результате моделирования схемы при проверке гипотезы решение может сходиться или расходиться. Если решение сходится, то по вычисленным значениям оценок величин сигналов принимают решение о принятии или отбрасывании рассматриваемой гипотезы. Причиной же расхождения процесса решения может быть как не соответствие самой рассматриваемой гипотезы фактической неисправности (что соответствует отбрасыванию гипотезы), так и неудачно выбранное начальное приближение, использованное при моделировании. Поэтому сначала ведут поиск неисправной подсхемы, анализируя лишь те гипотезы, для которых удается получить решение. Если точность локализации неисправности оказывается неудовлетворительной, то изменяя начальное приближение или используя другие численные методы, пытаются получить решение и для других гипотез, которые, в случае успеха, включают в рассмотрение.

Рис. 1. Алгоритм локализации неисправности подсхем ЭУ

Для снижения количества рассматриваемых подсхем может быть рекомендовано, ограничиваться лишь связными подсхемами. При этом для исключения экспоненциальной зависимости времени решения задачи разбиения схемы на подсхемы также следует применять эвристический подход, который заключается в том, что разбиение ЭУ на подсхемы, их анализ и выделение максимально больших подсхем производится не для всей цепи, а для ее отдельных частей, называемых блоками.

#### Выводы

Предложена конструктивная процедура и реализующий ее алгоритм формализованного представления процесса получения последовательности тестовых гипотез определения неисправной подсхемы ЭУ. Процедура позволяет исключить при диагностике полный прямой перебор всех подсхем ЭУ и, тем самым, сократить трудоемкость поиска неисправной подсхемы.

## Список литературы

- Андрусевич, А.А. Синтез тестопригодных схем путем устранения функциональноструктурной избыточности [Текст] / А.А. Андрусевич, И.Ш. Невлюдов, М.А. Бережная, М.Г. Рыжикова, Я.Ю. Королева // Вестник Академии инженерных наук Украины. Труды Государственного аэрокосмического университета им. Жуковского «ХАИ». - 2006. -№3 (30). - С. 188-192.

- 2. Андрусевич, А.А. Синтез системы автоматизированной диагностики цифровых модулей технологического оборудования [Текст] / А.А. Андрусевич, И.Ш. Невлюдов, Б.А. Шостак // Вісті Академії Інженерних наук України. 2004. №4(24). С. 125-132.

- 3. Скобцов, Ю.А. Генерация тестов для последовательностных схем с использованием кратной стратегии наблюдения выходных сигналов / Ю.А. Скобцов, В.Ю. Скобцов, Ш.Н. Хинди // Науковий вісник Чернівецького університету. (Серія «Фізика. Електроніка»). 2008. Вип. 423. С. 29 36.

- 4. Влах, И. Машинные методы анализа и проектирования электронных схем / И. Влах, К. Сингхал. М.: Радио и связь, 2007. 560 с.

- 5. Чуа, Л.О. Машинный анализ электронных схем: алгоритмы и вычислительные методы / Л.О. Чуа, П.-М. Лиин. М.: Энергия, 2008. 640 с.

- 6. Blum, C. Swarm Intelligence in Optimization. Introduction and Applications. Natural Computing Series / C. Blum, Li Xiaodong. Springer-Verlag Berlin Heidelberg, 2008. P. 43-85.

- 7. Diaz, E.A. Tabu Search Algorithm for Structural Software Testing Computers / E. Diaz, J. Tuya // Operations Research. 2008. No. 35 (10). P. 3052-3072.

#### ФОРМАЛІЗАЦІЯ ПРЕДСТАВЛЕННЯ ПОСЛІДОВНОСТІ ТЕСТОВИХ ГІПОТЕЗ ПРИ ЛІАГНОСТУВАННІ ЕЛЕКТРОННИХ СХЕМ

А.А. Верлань<sup>1</sup>, Ю. Стертен<sup>1</sup>, С.А. Положаенко<sup>2</sup>

<sup>1</sup> Норвезький університет науки та технологій, NTNU Gjøvik, Teknologiveien 22, 2815 Gjøvik, Norway; e-mail: andriy.verlan@ntnu.no <sup>2</sup> Одеський національний політехнічний університет,

просп. Шевченка, 1, Одеса, 65044, Україна; e-mail: polozhaenko@mail.ru

Розроблено процедуру формалізованого представлення послідовності пробних (тестових) гіпотез в ході перевірки працездатності електронних пристроїв при їх декомпозиції на підсхеми. Процедуру доведено до практичного алгоритму, який забезпечує ефективний (з точки зору мінімізації трудовитрат) пошук несправних підсхем електронного пристрою.

**Ключові слова**: електронний пристрій, підсхема, діагностика, тестова гіпотеза, навчаюча послідовність, алгоритм пошуку несправності

# FORMALIZED REPRESENTATION SEQUENCES OF TEST HYPOTHESES IN THE DIAGNOSIS OF ELECTRONIC CIRCUITS

A. Verlan<sup>1</sup>, Yu. Sterten<sup>1</sup>, S. Polozhaenko<sup>2</sup>

<sup>1</sup> Norwegian University of Science and Technology NTNU Gjøvik, Teknologiveien 22, 2815 Gjøvik, Norway; e-mail: andriy.verlan@ntnu.no <sup>2</sup> Odesa National Glytechnic University,

1 Shevchenko Str., Odesa, 65044, Ukraine; e-mail: savichsp@gmail.com

The procedure of formalized representation of a sequence of test hypotheses in the verifying operation of electronic devices when they are decomposing in the sub circuit. The procedure brought to a practical algorithm, providing an efficient (in terms of minimizing labour input) troubleshooting sub circuits electronic device.

**Keywords**: electronic device sub circuit, diagnostics, test the hypothesis, the training sequence, fault localization algorithm.