Ю.М. Коростиль, С.Я. Гильгурт, г. Киев

# ПЕРСПЕКТИВЫ РАЗВИТИЯ РЕКОНФИГУРИРУЕМЫХ ВЫЧИСЛИТЕЛЕЙ ДЛЯ ВЫПОЛНЕНИЯ РЕСУРСОЕМКИХ РАСЧЕТОВ

**Abstract.** The future of the reconfigurable accelerators is discussed. The technical solutions of Convey Computer company as examples of resolving problems are analyzed.

### Ввеление

При выполнении инженерных и научных расчетов в настоящее время все большее применение находят высокопроизводительные вычислительные средства, которые постепенно становятся изделиями массового использования.

Высокая стоимость возможности И скромные масштабирования "классических" суперкомпьютеров привели к широкому распространению кластерных решений, позволяющих за счет использования стандартных компонентов и технологий существенно снизить стоимость владения вычислительным оборудованием. К сожалению, в силу архитектурных особенностей, традиционные кластерные решения не покрывают весь спектр вычислительных задач, с которыми сталкиваются исследователи и производственники. По этой причине возникло и активно развивается направление, связанное с применением различного рода присоединенных вычислителей и ускорителей, которыми оснащаются вычислительные узлы кластеров. Основой подобных устройств служат компоненты с высокой степенью внутреннего параллелизма - многоядерные кристаллы наподобие Intel Xeon Phi, графические процессоры общего применения (GPGPU), программируемые логические интегральные схемы (ПЛИС).

Анализ информационных источников свидетельствует, что плотная концентрация процессорных элементов, свойственная таким изделиям, позволяет эффективно реализовывать тесносвязанные вычислительные алгоритмы. Но при этом возникает другая существенная проблема — узким местом становится взаимодействие со стандартными компонентами вычислительной системы, то есть, с вычислительными узлами кластера. Как следствие, возникают сложности при масштабировании подобных решений. К тому же, применение непривычных для большинства программистов архитектур усложняет и замедляет процесс разработки программного обеспечения для них. В наибольшей степени данное противоречие проявляется при использовании реконфигурируемых вычислителей на базе ПЛИС, которые, с одной стороны, позволяют наиболее гибко подстраиваться под нужды прикладных задач, с другой — требуют трудоемкого процесса

разработки конфигураций для микросхем программируемой логики [1, 2].

В настоящей работе на примере решений, примененных в изделиях фирмы Convey Computer [3], рассмотрены перспективные направления развития реконфигурируемых вычислителей, позволяющие в значительной степени преодолеть сформулированное выше противоречие.

## 1. Основные проблемы

Анализ известных разработок в области реконфигурируемых вычислителей позволяет выделить следующие технические проблемы, с которыми приходится сталкиваться при повышении их производительности:

- выбор интерфейса обмена данными с материнской системой (хост-системой);

- конструктивные ограничения на объем оборудования (кристаллов ПЛИС и ОЗУ), которое может быть размещено на присоединенном устройстве;

- повышение объема локальной оперативной памяти без снижения эффективности ее функционирования.

В качестве интерфейса между реконфигурируемым вычислителем и хост-системой могут выступать внешние коммуникационные каналы (Ethernet, USB), периферийные интерфейсы (ATA, SATA, SCSI), системные шины (PCI, PCI Express) и даже шины доступа к памяти (DDR2, DDR3) [4]. Но наиболее высокую пропускную способность обеспечивают шины межпроцессорного обмена (HyperTransport, QPI), при разработке которых изначально закладывалась возможность совместной работы с реконфигурируемыми вычислителями.

Конструктивно сопроцессор может быть выполнен в виде внешнего (по отношению к вычислительному узлу) модуля, если в качестве интерфейса используется коммуникационный канал. В этом случае на объем оборудования, практически, не накладывается ограничений, просто решаются вопросы питания. Однако, скорость связи с хост-системой у такого варианта самая низкая. При выборе более быстрых интерфейсов реконфигурируемый вычислитель располагается непосредственно внутри вычислительного модуля, что резко сокращает его габариты. Как следствие, на объем компонентов, которые могут быть включены в состав сопроцессора, накладываются жесткие ограничения. При этом наблюдается тенденция уменьшения размеров вычислителя по мере ускорения обмена. В самом деле, плата расширения, вставляемая в системную шину, может иметь большие габариты, чем модуль, устанавливаемый в слот памяти. На размеры сопроцессора, вставляемого в процессорный сокет, накладываются еще более строгие ограничения.

Оперативная память на протяжении всей истории развития вычислительной техники является одним из самых проблемных компьютерных компонентов. Сильная обратная зависимость цены от показателей емкости элементной базы ОЗУ вынуждает разработчиков задействовать механизмы кэширования, приводящие к сложной многоуровневой иерархии подсистемы памяти. В реконфигурируемых вычислителях данные проблемы встают еще более остро. К сложностям кэширования добавляются конструктивные ограничения на объем, а также вопросы согласования по данным локального ОЗУ сопроцессора с основной памятью хост-системы. Но наиболее болезненной проблемой в данной связи, по-видимому, является существенное усложнение труда программистов, вынужденных иметь дело с локальной памятью сопроцессора.

Помимо рассмотренных выше технических сложностей, сопроцессорам на программируемой логике присущи также недостатки, свойственные реконфигурируемым вычислениям в целом. В частности, при разработке прикладных программ пользователю приходится синтезированной в ПЛИС нестандартной архитектурой. При написании наиболее ресурсоемкой части кода, предназначенной для реализации на реконфигурируемом вычислителе, весь огромный багаж инструментального и системного ПО, созданный за несколько десятилетий для широко распространенных компьютеров на базе Intel-совместимых процессоров, становится бесполезным. Теоретически, для каждой новой конфигурации, загружаемой в ПЛИС, необходимо разрабатывать новые операционные системы, компиляторы, отладчики и др. вспомогательные программные средства, ориентированные на эту конкретную вычислительную структуру. Другими словами, при создании реконфигурируемых вычислителей важную роль играют вопросы унификации и стандартизации, в том числе инструментального и системного программного обеспечения.

## 2. Решения фирмы Convey Computer

Рассмотрим, как решаются перечисленные выше технические задачи в изделиях фирмы Convey Computer, одного из лидеров в области создания высокопроизводительных компьютерных систем, ключевыми компонентами которых являются реконфигурируемые вычислители.

2.1. Выбор интерфейса и конструктивного решения. В линейке изделий НС-1, НС-1ех, НС-2, НС-2ех, МХ-100 данной компании в качестве хост-систем используются двухсокетные серверные платформы под процессоры семейства Intel Xeon [5, 6]. Для достижения максимальной пропускной способности в качестве интерфейса связи материнской платы и реконфигурируемого вычислителя используется межпроцессорная шина QPI. Физически сопроцессор подключен через коннектор, вставляемый в свободный сокет материнской платы вместо второго процессора.

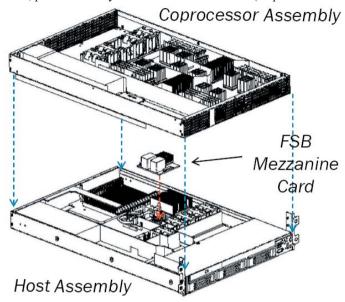

Противоречие между высокопроизводительным интерфейсом и малыми габаритами соответствующего разъема решено следующим образом. Реконфигурируемый вычислитель изготовлен в виде отдельного серверного модуля, устанавливаемого непосредственно над хост-системой, как показано на рисунке 1 [7].

При этом в процессорный разъем хост-системы (Host Assembly) вставляется компонент (FSB Mezzanine Card), являющийся частью высокоскоростного цифрового канала, передающего данные по шлейфу на его ответную часть, расположенную на плате вычислителя (Coprocessor Assembly).

Рис. 1. Конструктивное исполнение реконфигурируемого вычислителя

**2.2 Подсистема оперативной памяти.** Рассмотрим теперь способы решения более серьезных проблем, связанных с эффективной реализацией подсистемы локального ОЗУ реконфигурируемого вычислителя.

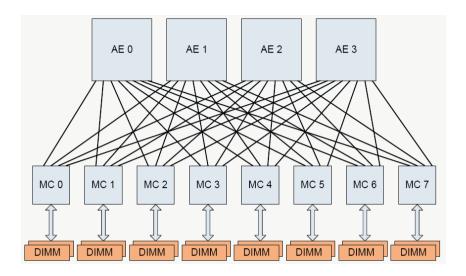

На рисунке 2 приведена схема взаимосвязей между основными вычислительными компонентами сопроцессоров Convey Computer [8].

Реконфигурируемые ресурсы, доступные для загрузки пользовательских вычислительных структур представляют собой четыре СБИС программируемой логики семейства Virtex-5 или Virtex-6 фирмы Xilinx (в зависимости от модели сопроцессора). Разработчики назвали эти ПЛИС ядрами приложений (ЯП) – application engine (АЕ). Разрабатываемым пользователями конфигурациям специалисты фирмы Convey дали название "персонализация" – "personality". Каждый кристалл ЯП связан с каждым из восьми контроллеров памяти (КП) – memory controller (МС) по скоростному каналу производительностью в 2,5 Гбайт/сек. Каждый контроллер памяти, в свою очередь, обменивается данными с двумя стандартными слотами DIMM на скорости 5 Гбайт/сек. Следовательно, в случае отсутствия конфликтов, интенсивность обмена информацией между ядром приложения и модулями DIMM может достигать своего пикового значения в 20 Гбайт/сек.

Рис.2. Взаимосвязь между основными вычислительными компонентами

Таким образом, общая пиковая пропускная способность подсистемы памяти составляет 80 Гбайт/сек. В самом худшем случае, при одновременном обращении всех ЯП к одному и тому же модулю памяти величина быстродействия канала обмена слота DIMM с КП, равная 5 Гбайт/сек, будет поровну делиться между ядрами и снизится до 1,25 Гбайт/сек.

Отметим, что контроллеры памяти также реализованы на ПЛИС фирмы Xilinx, а в слоты DIMM могут быть установлены как стандартные модули памяти емкостью 1 Гб, 2Гб или 4 Гб, так и специально созданные фирмой Convey устройства памяти, названные разработчиками модулями SG-DIMM. Каждый такой модуль содержит помимо микросхем памяти одну ПЛИС фирмы Altera и реализует более эффективную по сравнению с обычными модулями обработку запросов к произвольным адресам, основанную на методе scatter-gather.

Как указывалось выше, одной из существенных проблем при работе с присоединенными сопроцессорами является сложность взаимодействия нескольких видов памяти. Как минимум, пользователю приходится иметь дело с общей памятью хост-системы (физически расположенной на материнской плате сервера или персонального компьютера) и с локальной памятью сопроцессора. Пересылка данных из общего ОЗУ в локальное и обратно требует, с одной стороны, усилий программиста, с другой — служит источником значительных временных задержек, способных свести на нет преимущества использования сопроцессора.

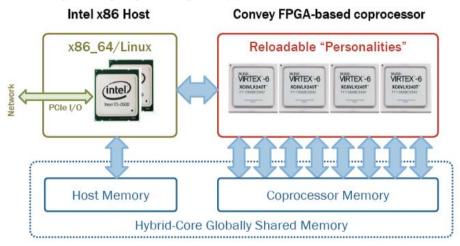

Разработчики фирмы Convey решили данную проблему следующим образом. Вся физическая локальная память реконфигурируемого вычислителя логически отображается в общую память, доступную программам, выполняемым на центральном процессоре хост-системы, образуя с ней единое адресное пространство (рис.3) [9].

Рис.3. Логическая структура совместно используемой памяти

Для обеспечения такой возможности между двумя видами памяти организован скоростной кэш-когерентный канал обмена данными. При этом используются механизмы, специально заложенные для данных целей в межпроцессорную шину.

Физически канал обмена реализован посредством еще одной ПЛИС, которая расположена на реконфигурируемом вычислителе и названа разработчиками хабом ядер приложений (ХЯП) – Application Engine Hub (АЕН).

В результате такого решения и общее ОЗУ, и локальная память сопроцессора представляется для программиста в виде единого виртуального запоминающего устройства, что существенно упрощает работу с реконфигурируемым вычислителем.

2.3 Применение стандартного программного обеспечения. Унифицировать процесс создания программного обеспечения для изделий фирмы Convey и обеспечить разработчикам возможность максимально использовать богатый опыт программирования стандартных процессоров позволяет следующее решение. В состав реконфигурируемого вычислителя включен так называемый скалярный процессор (СП), способный выполнять помимо

фиксированного набора команд, специальные инструкции, позволяющие управлять вычислительными структурами, синтезированными в ПЛИС ядер приложений [10]. Физически данный процессор реализован на той же ПЛИС, что и упомянутый выше узел ХЯП.

Примечательно, что при организации вычислительного процесса, с одной стороны, СП выступает в роли сопроцессора по отношению к хостсистеме на базе стандартного Intel-совместимого процессора. С другой стороны, вычислительные структуры, загруженные в узлы ЯП, выступают в качестве сопроцессоров по отношению к СП. Двухуровневая организация взаимодействия центрального процессора с реконфигурируемыми ресурсами позволила реализовать такую программную модель, при которой те команды, которые не могут быть выполнены на скалярном процессоре, передаются на исполнение ядрам приложений, синтезированным в ПЛИС. Физически СП имеет непосредственную связь с каждым из четырех ЯП, обеспечивая засылку в них параметров, полученных от центрального процессора, и передачу в обратном направлении статусной информации.

Описанное выше техническое решение позволило разработчикам фирмы Convey обеспечить пользователей необходимым инструментарием для эффективного создания и отладки программного обеспечения. Если пользователь не имеет возможности создавать собственные конфигурации для ПЛИС, он может воспользоваться рядом уже созданных и отлаженных "персонализаций", для которых разработаны соответствующие компиляторы языков C, C++ и ФОРТРАН. Фирма Convey организовала сообщество заинтересованных разработчиков, создающих конфигурации для различных прикладных областей. Пользователям, занимающимся созданием "персонализаций", также предлагается соответствующий эффективный инструментарий.

В заключение заметим, что данный подход в совокупности с описанной ранее подсистемой виртуальной кэш-когерентной памяти позволяет пользователям при работе с реконфигурируемыми вычислителями фирмы Convey применять (с небольшими модификациями) такую эффективную и распространенную технологию параллельного программирования, как OpenMP.

#### Выводы

В результате проведенного исследования на примере разработок фирмы Convey Computer показана возможность эффективного разрешения основных технических трудностей и противоречий, свойственных реконфигурируемым вычислителям.

Можно также констатировать, что разработки, подобные созданным данной компанией линейке гибридных вычислительных систем на базе программируемой логики, являются не просто серверными платформами,

оборудованными реконфигурируемыми сопроцессорами, а, фактически, полноценными суперкомпьютерными комплексами, превосходящими по скоростным характеристикам традиционные кластерные структуры при решении ряда тесносвязанных вычислительных задач.

В качестве дальнейшего развития рассмотренных систем, в частности, инструментального программного обеспечения для них, можно предположить переход на использование стандарта OpenCL, о перспективности которого при создании реконфигурируемых средств говорилось в работе [11]. 1. Реконфигурируемые вычислительные системы: Основы и приложения. / А.В. Палагин, В.Н. Опанасенко. – К.: «Просвіта», 2006. – 280 с.

- 2. *Каляев И.А., Левин И.И., Семерников Е.А., Шмойлов В.И.* Реконфигурируемые мультиконвейерные вычислительные структуры / Под общ.ред. И.А.Каляева. Ростов н.Д: Издательство ЮНЦ РАН, 2008. 320 с.

- 3. Convey Computer [Электронный ресурс]. Режим доступа: http://www.conveycomputer.com. Загл. с экрана. (Дата обращения: 17.02.2013).

- 4. *Гильгурт С.Я.* Обзор современных реконфигурируемых унифицированных вычислителей // Моделювання та інформаційні технології. Зб. наук. пр. ІПМЕ НАН України. Вип. 49. Київ: 2008. С. 17–24.

- 5. Convey: Better Computing for Better Analytics // Convey Computer Corporation. Convey White Paper. 4р. [Электронный ресурс]. Режим доступа: http://www.conveycomputer.com/files/3613/5085/4052/Convey\_HC-2\_Product\_Brochure.pdf. Загл. с экрана. (Дата обращения: 17.02.2013).

- 6. Convey MX Series. Architectural Overview // Convey Computer Corporation. Convey White Paper. 10р. [Электронный ресурс]. Режим доступа: http://www.conveycomputer.com/files/5913/5266/3278/CONV-12-036.1MXarchOvrvwWeb.pdf. Загл. с экрана. (Дата обращения: 17.02.2013).

- 7. *Mutke E.M.* Putting Personality Into High Performance Computing // Frühjahrstreffen des ZKI-Arbeitskreises. "Supercomputing". 19-20 Mai 2011. DESY, Zeuthen.

- 8. Convey Personality Development Kit Reference Manual // Convey Computer Corporation. 109р. [Электронный ресурс]. Version. 5.2. Режим доступа: http://wikis.ece.iastate.edu/cpre584/images/6/64/ConveyPDKReferenceManual.pdf. Загл. с экрана. (Дата обращения: 17.02.2013).

- 9. Hybrid Core Computing and Bioinformatics Applications // Convey Computer Corporation. 31р. [Электронный ресурс]. Last Update: 12/10/2012. Режим доступа: http://hpcsociety.org/Resources/Documents/121212Kirby-CONVEY-SHPCP\_121212. pdf. Загл. с экрана. (Дата обращения: 17.02.2013).

- 10. *Bakos J.D.* High-Performance Heterogeneous Computing with the Convey HC-1 // Computing in Science and Engineering, vol. 12, no. 6, pp. 80–87, 2010.

- 11.  $\Gamma$ ильгурт C.Я. О применении стандарта OpenCL для создания реконфигурируемых устройств на базе ПЛИС // 3б. наук. пр. ІПМЕ НАН України. Київ, 2012. Вип. 62. С. 3–11.