# БЫСТРОДЕЙСТВУЮЩИЙ СЧЕТЧИК ИМПУЛЬСОВ НА ОСНОВЕ КОДОВ ФИБОНАЧЧИ

**А. А. Борисенко,**  $\partial$ -р техн. наук, профессор;

С. М. Маценко, аспирант,

Сумский государственный университет,

ул. Римского-Корсакова, 2, г. Сумы, 40007, Украина;

E-mail: s.matsenko@mail.ru

В данной статье рассмотрен помехоустойчивый счетчик Фибоначчи с повышенным быстродействием, которое достигается за счет введения новых элементов и связей. Повышение быстродействия происходит путем образования сигнала параллельного переноса в связи с введением дополнительных входов цифровых элементов, что позволяет существенно сократить распространение сигналов в схеме.

**Ключевые слова**: цифровой счетчик, быстродействие, фибоначчиевые числа, помехоустойчивость, надежность.

## ВВЕДЕНИЕ И ПОСТАНОВКА ЗАДАЧИ

Расширение областей применения цифровых приборов в процессе внедрения их в электронные устройства приводит к повышению требований к обеспечению надежности, помехоустойчивости, быстродействия и достоверности работы сложных электронных систем которые их используют. Одними из устройств цифровой техники, применяемых в таких системах, являются цифровые счетчики импульсов.

Во многих случаях важно, чтобы схемы цифровых счетчиков импульсов обладали высокой надежностью и, частности, Такими помехоустойчивостью быстродействием. и пифроврии устройствами могут являться счетчики, работающие в двоичной системе счисления, которые могут обнаруживать, а в некоторых случаях исправлять, ошибки [1-6]. Недостатками данных счетчиков являются большие аппаратурные затраты на реализацию данного свойства. С целью повышения помехоустойчивости используется кодирование на основе избыточных кодов, которое защищает отдельные блоки проектируемого устройства от помех [7].

В настоящее время разработаны различные методы повышения надежности работы цифровых систем, которые предложены H. C. Щербаковым [8]. Способы достоверности повышения функционирования цифровых устройств предложены Г. В. Куно [9]. Повышение надежности цифровых устройств с помощью применения кодирования избыточного рассмотрены Я. А. Хетагурова [10]. Методы построения отказоустойчивых дискретных устройств на основе корректирующих кодов приведены в работах А. А. Павлова, А. Н. Кузнецова [11]. Большой вклад в повышения помехоустойчивости и надежности работы цифровых устройств на основе биномиальных кодов разработаны А. А. Борисенко [12]. Решение проблемы создания надежных систем управления помошью информационной избыточности путем применения кодов Фибоначчи были предложены А. П. Стаховым [13].

Немаловажным критерием при выборе и использовании цифровых счетчиков импульсов является их быстродействие, поэтому повышение этого критерия является очень важной и актуальной задачей.

В статье [14] был предложен счетчик Фибоначчи, работающий в минимальных фибоначчиевых кодах, однако он имеет недостаточно высокое быстродействие из-за наличия в нем последовательных цепей связи. Задачей данной статьи является повышения его быстродействия за счет введения новых элементов и связей. Повышение быстродействия происходит за счет образования сигнала параллельного переноса в связи с введением дополнительных входов цифровых элементов, что позволяет существенно сократить распространение сигналов в схеме.

# РЕАЛИЗАЦИЯ СЧЕТЧИКА

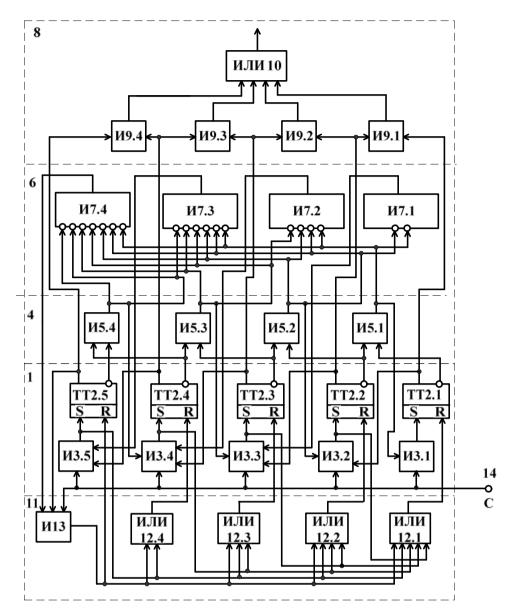

Схема пятиразрядного счетчика Фибоначчи, представленная на рис. 1, содержит в своей структуре следующие функциональные блоки: регистр 1, блок анализа 4, блок диспозиции 6, блок контроля 8, блок установки в нуль 11 и шину тактовых импульсов (ТИ) 14. Регистр счетчика импульсов содержит п триггеров и п элементов И, п-1 элементов И, создающих блок анализа, n-1 элементов И с инверторами на входах, создающих блок диспозиций, n-1 элементов И, объединенных элементом ИЛИ, создающих блок контроля, n-1 элементов ИЛИ и элемент И, к первому входу которого подключена шина тактовых импульсов (ТИ), создающих блок установки в нуль. Выходы п-1 элементов И блока анализа 4 соединены с первыми входами n-1 элементов и регистра 1, на вторые входы этих элементов и на первый вход элемента И блока установки в нуль 11 поступает тактовый сигнал с входной шины тактовых импульсов (ТИ) 14, сигнал с прямых выходов триггеров n-1 элементов поступает на третьи входы элементов И, четвертые входы которых соединены с выходами n-2 элементов и блока диспозиций 6, выход n-1-го элемента И блока диспозиций 6 соединен с третьим входом элемента И блока установки в нуль 11, выходы элементов И регистра 1 соединены с входами установки триггеров в единичное состояние. Инверсные выходы триггеров соединены с первыми и вторыми входами n-1 элементов и блока анализа 6, прямые выходы триггеров соединены с первыми и вторыми входами n-1 элементов И блока контроля 8, прямой выход n-го триггера соединен со вторым входом элемента И блока установки в нуль 11, выходы элементов И блока контроля 8 соединены с входом элемента ИЛИ.

Первый вход элемента НЕ первого разряда соединен с первыми входом элемента НЕ первого, второго, третьего и п-1-го разряда блока лиспозиций 6 и соединены с выходом элемента И первого разряда блока анализа 4, второй вход этого элемента является вторым входом второго третьего, n-1-го элементов НЕ блока диспозиций 6 и соединен с выходом элемента И второго разряда блока анализа 4, выходы элементов НЕ первого разряда соединены с двухвходовым элементом I блока диспозиций 6. Третий вход элемента НЕ второго разряда соединен с третьим входом элемента НЕ третьего и п-1-го разрядов, которые соединены с выходом элемента И второго разряда, четвертый вход элемента HE второго разряда соединен с четвертым входом третьего и n-1 разрядов элементов НЕ и с выходом элемента И третьего разряда, выходы элементов HE второго разряда соединены с четырехвходовым элементом I блока диспозиций 6. Пятый вход элемента НЕ третьего разряда соединен с пятым входом элемента НЕ n-1-го разряда и с выходом элемента И третьего разряда, k-1 вход элемента НЕ третьего разряда соединен с k-1 входом элемента НЕ n-1-го разряда и с выходом элемента И n-1-го разряда, выходы элементов НЕ третьего разряда соединены с шестивходовым элементом I блока диспозиции 6, k вход элемента НЕ n-1-го разряда соединен с выходом элемента И n -1-го разряда блока анализа, выходы элементов HE n-1-го разряда соединены с семивходовым элементом I блока диспозиции.

Рисунок 1 — Быстродействующий счетчик импульсов на основе кодов Фибоначчи

Выход второго элемента И регистра 1 соединен с k входом первого элемента ИЛИ блока установки в нуль 11, k-1 вход первого элемента ИЛИ соединен с k-1 входом второго элемента ИЛИ и с выходом третьего элемента И регистра 1, k-2 вход первого элемента ИЛИ соединен с k-2 входом второго элемента ИЛИ, с k-2 входом третьего элемента ИЛИ и с выходом элемента И п-1-го разряда регистра 1, k-3 вход первого элемента ИЛИ соединен с k-3 входами вторых третьих и четвертых элементов ИЛИ блока установки в нуль 11 и с выходом п-го элемента И регистра 1, k-4 вход первого элемента ИЛИ с k-4 входами второго, третьего и четвертого элементов ИЛИ блока установки в нуль 11, с входом установки в нулевое состояние п-го триггера регистра 1 и с выходом элемента И блока установки в нуль 11. Выходы n-1 элементов ИЛИ блока установки в нуль

11 соединены с входами установки в нулевое состояние n-1 триггеров регистра 1.

Регистр 1 состоит из триггеров TT2.1 – TT2.5, и схем ИЗ.1 – ИЗ.5, в блок анализа 4 входят двухвходовые схемы И5.1 – И5.4 анализирующий выходы двух рядом стоящих триггеров, а также один из входов рядом стоящего двухвходового элемента И5.1 – И5.4. Данный блок параллельно производит операции сравнения в младших четырех разрядах и предназначен для обнаружения в них двух рядом стоящих единиц. В устройстве содержится блок диспозиции 6, состоящий из схем И7.1 – И7.4 с инверторами на входах, который контролирует выходы блока анализа 4.

Также схема содержит блок контроля 8, выполненный на схемах И9.1 — И9.4, выходы которые объединены схемой ИЛИ10, блок установки нуля 11, имеющий в своей структуре схемы ИЛИ12.1 — ИЛИ12.4 и устанавливающий регистр 4 в исходное состояние, вспомогательную схему И13, которая предназначена для окончания процесса счета, шину 14 тактовых импульсов (ТИ).

Быстродействующий счетчик импульсов на основе кодов Фибоначчи работает следующим образом. Первоначально все триггеры регистра 1 находятся в нулевом состоянии. Первый тактовый импульс с шины 14 устанавливает первый триггер регистра TT2.1 в 1 и запрещает прохождение разрешающего сигнала на остальные триггеры схемы TT2.2 - TT2.5. При поступлении второго тактового импульса, второй триггер регистра TT2.2 устанавливается в 1, так подается разрешающий сигнал с выхода первого триггера TT2.1, одновременно устанавливается в 0 через блок установки нуля 11. Третий тактовый импульс устанавливает в единичное состояние только третий триггер схемы ТТ2.3, так как разрешающие сигналы на него подаются с блока диспозиции 6 блока анализа 4 и второго триггера TT2.2, при этом первый и второй триггеры TT2.1 - TT2.2 устанавливаются в нуль сигналом с блока установки нуля 11. Четвертый тактовый импульс устанавливает триггер TT2.1 в единичное состояние, при этом триггеры TT2.1 - TT2.3 находятся в соответствующим сигналом с блока диспозиции 6. Данная процедура повторяется до тех пор, пока не будет получена кодовая комбинация, в которой между двумя единицами будет находиться один нуль.

Счетчик Фибоначчи функционирует в соответствии с табл.1.

Рассмотрим работу быстродействующего счетчика на основе кодов Фибоначчи более подробно.

В исходном состоянии все триггеры регистра 1 находятся в нуле, что соответствует кодовой комбинации 00000. При поступлении первого тактового импульса осуществляется запись 1 в младший триггер регистра через первый вход схемы ИЗ.1, на который подается разрешающий сигнал с шины 14, на второй вход ИЗ.1 подается единица с выхода схемы И5.1, при этом получаем следующую кодовую комбинацию 00001. Остальные триггеры TT2.2 – TT2.5 находятся в нулевом состоянии, так как на первые входы схем ИЗ.2 – ИЗ.5 подаются нулевые сигналы с прямых выходов триггеров TT2.1 - TT2.4. Наличие 1 в первом разряде и нулей в остальных разрядах дает возможность записи 1 во второй разряд при поступлении второго тактового импульса, при этом единичный сигнал с прямого выхода триггера TT2.1 поступает на третий вход схемы ИЗ.2, на первый вход которой одновременно поступает сигнал с выхода схемы И5.2 блока анализа 4, на входы которой с инверсных выходов триггеров TT2.1, TT2.3 регистра подаются две 1. Одновременно 1 с выхода схемы ИЗ.2 подается на первый вход схемы ИЛИ12.1 блока установки нуля 11, на остальные входы которой поступают нулевые сигналы со схем ИЗ.3 - ИЗ.5, так как остальные триггеры TT2.3 - TT2.5

находятся в нулевом состоянии. В результате единичный сигнал поступит на вход установки нуля первого триггера TT2.1, таким образом получаем кодовую комбинацию 00010.

Tаблица 1 — Кодовые состояния быстродействующего счетчика импульсов в кодах Фибоначчи k=5

|    |   | 1 |                |   | 2 |                |   | 3 |                |   | 4 |                |   | 5 |                | $\boldsymbol{F}_{k}$ |

|----|---|---|----------------|---|---|----------------|---|---|----------------|---|---|----------------|---|---|----------------|----------------------|

|    | S | R | $\mathbf{Q_1}$ | S | R | $\mathbf{Q_2}$ | S | R | $\mathbf{Q}_3$ | s | R | $\mathbf{Q_4}$ | S | R | $\mathbf{Q_5}$ | 54321                |

| 0  | 0 | 0 | 0              | 0 | 0 | 0              | 0 | 0 | 0              | 0 | 0 | 0              | 0 | 0 | 0              | 00000                |

| 1  | 1 | 0 | 1              | 0 | 0 | 0              | 0 | 0 | 0              | 0 | 0 | 0              | 0 | 0 | 0              | 00001                |

| 2  | 0 | 1 | 0              | 1 | 0 | 1              | 0 | 0 | 0              | 0 | 0 | 0              | 0 | 0 | 0              | 00010                |

| 3  | 0 | 0 | 0              | 0 | 1 | 0              | 1 | 0 | 1              | 0 | 0 | 0              | 0 | 0 | 0              | 00100                |

| 4  | 1 | 0 | 1              | 0 | 0 | 0              | 1 | 0 | 1              | 0 | 0 | 0              | 0 | 0 | 0              | 00101                |

| 5  | 0 | 0 | 0              | 0 | 1 | 0              | 0 | 1 | 0              | 1 | 0 | 1              | 0 | 0 | 0              | 01000                |

| 6  | 1 | 0 | 1              | 0 | 1 | 0              | 0 | 1 | 0              | 1 | 0 | 1              | 0 | 0 | 0              | 01001                |

| 7  | 0 | 1 | 0              | 1 | 0 | 1              | 0 | 1 | 0              | 1 | 0 | 1              | 0 | 0 | 0              | 01010                |

| 8  | 0 | 0 | 0              | 0 | 0 | 0              | 0 | 0 | 0              | 0 | 0 | 0              | 1 | 0 | 1              | 10000                |

| 9  | 1 | 0 | 1              | 0 | 1 | 0              | 0 | 1 | 0              | 0 | 1 | 0              | 1 | 0 | 1              | 10001                |

| 10 | 0 | 0 | 0              | 1 | 0 | 1              | 0 | 1 | 0              | 0 | 1 | 0              | 1 | 0 | 1              | 10010                |

| 11 | 0 | 0 | 0              | 0 | 0 | 0              | 1 | 0 | 1              | 0 | 0 | 0              | 1 | 0 | 1              | 10100                |

| 12 | 1 | 0 | 1              | 0 | 0 | 0              | 1 | 0 | 1              | 0 | 0 | 0              | 1 | 0 | 1              | 10101                |

Третий тактовый импульс устанавливает триггер TT2.3 в единичное состояние. Это происходит потому, что на третий вход схемы ИЗ.3 подается единичный сигнал с прямого выхода триггера ТТ2.2, на первый вход которого поступает сигнал с выхода схемы И5.3, так как с инверсных выходов триггеров TT2.3, TT2.4 на вход И5.3 поступает 1. На четвертый вход схемы ИЗ.З поступает 1 с выхода схемы И7.1 блока диспозиции 6, так как на вход схемы ИЗ.2 подается нулевой сигнал с выхода прямого триггера TT2.1, в результате чего на инверсных выходах триггеров TT2.1 и TT2.2 будет нулевой сигнал который поступает на схему И5.1 блока анализа 4, а с ее выхода на схему НЕ, после чего сигнал подается на схему И7.1. Одновременно с выхода схемы И3.3. единичный сигнал поступает на первый вход элемент ИЛИ12.2 и с ее выхода на второй вход ИЛИ12.1 блока установки нуля 11, выход которой соединен с установочным входом в 0 всех триггеров TT2.1 - TT2.5. Таким образом произойдет сброс триггеров TT2.1 и TT2.2 в 0. Этот переход соответствует состоянию счетчика 00100.

Поступление четвертого тактового импульса приводит к установке в единичное состояние триггеров ТТ2.1 и ТТ2.3 регистра 1. В этом случае триггер ТТ2.1 устанавливается в единичное состояние, так как на первый вход схемы ИЗ.1 поступает единичный сигнал с шины 14, а на второй вход разрешающий сигнал с выхода схемы И5.1 блока анализа 4. С

инверсного выхода триггера TT2.1 на второй вход схемы И5.1 подается 1, на второй вход этой схемы подается 0 с инверсного выхода триггера TT2.2. Таким образом на вход схемы И5.1 поступает нулевой сигнал, который поступает на второй вход схемы НЕ, на первый вход которой подается 0 с выхода схемы И5.2, после чего подается на схему И7.1. В связи с имеющимся на входе схемы И7.1 блока диспозиции 6 входных инверторов, на выходе схемы будет присутствовать единичный сигнал, поступающий на четвертый вход схемы И3.3. Единичный сигнал с выхода триггера TT2.1 подается на элемент И9.1 и поступает на третий вход схемы И3.3. На первый вход этой схемы подается сигнал 1 с выхода схемы И5.3. Триггер TT2.2 будет находиться в нулевом состоянии сигналом с выхода схемы И5.2. В результате будет получена комбинация 00101. Все последующие состояния счетчика происходят в соответствии с вышеописанным методом. Счет будет производиться до получения максимального фибоначчиевого числа 10101.

После появления максимального фибоначчиевого числа на выходе схемы И7.4 блока диспозиции 6 появится 1, которая совместно с 1 на прямом выходе триггера ТТ2.5 подается на вход элемента И13 и устанавливает все триггеры ТТ2.1 — ТТ2.5 регистра 1 в нулевое состояние. После этого счет заканчивается, регистр устанавливается в нулевое состояние, после чего начинается новый цикл счета.

Имеющиеся в устройстве последовательно соединенные двухвходовые И9.1 — И9.4 блока контроля служат для анализа правильности работы счетчика, выходы которых объединены схемой ИЛИ10, а входы подсоединены к прямым выходам двух рядом стоящий триггеров. Если в результате счета произойдет ошибка, что характеризуется появлением двух рядом стоящих единиц в разрядах фибоначчиевого числа, то одна из схем И9.1 — И9.4 откроется и на выходе схемы ИЛИ10 появится сигнал ошибки.

Таким образом, из-за наличия параллельных цепей сигналов переноса в блоке диспозиции 6 и блоке установки в нуль 11, позволяет существенно повысить быстродействие счетчика Фибоначчи, а использование в основе устройства фибоначчиевых чисел определяет его преимущество перед двоичными счетчиками в критерии помехоустойчивости.

# выволы

В данной работе был рассмотрен помехоустойчивый счетчик Фибоначчи с повышенным быстродействием. Счетчик работает в минимальных кодах Фибоначчи, обладает повышенным быстродействием, однородной структурой и способностью обнаруживать ошибки в процессе работы. Повышение быстродействия достигается за счет образования сигналов параллельного переноса в блоках диспозиции и установки в нуль в связи с введением дополнительных входов цифровых элементов.

# SUMMARY

## FAST IPULSE COUNTER BASED ON FIBONACCI CODE

A. A. Borisenko, S. M. Matsenko,

Sumy State University,

2, Rymsky-Korsakov Str., 40007, Sumy, Ukraine;

E-mail: s.matsenko@mail.ru

This paper presents a discussion of the noise-immune Fibonacci counter with increased operating speed, which is achieved by the introduction of new elements and connections. Speed improvement occurs through the formation of a signal translation due to the introduction of additional inputs of digital elements, which can significantly reduce the spread of signals in the circuit.

Keywords: digital counter, performance, Fibonacci numbers, error detection, reliability.

## ШВИДКОДІЮЧИЙ ЛІЧИЛЬНИК ІМПУЛЬСІВ НА ОСНОВІ КОДІВ ФІБОНАЧЧІ

## О. А. Борисенко, С. М. Маценко,

Сумський державний університет,

вул. Римського-Корсакова, 2, м. Суми, 40007, Україна;

E-mail: s.matsenko @ mail.ru

У статті розглянуто перешкодостійкий лічильник Фібоначчі з підвищеною швидкодією, яка досягається за рахунок введення нових елементів і зв'язків. Підвищення швидкодії відбувається шляхом утворення сигналу паралельного перенесення у зв'язку з введенням додаткових входів цифрових елементів, що дозволяє істотно скоротити поширення сигналів в схемі.

**Ключові слова**: цифровий лічильник, швидкодія, фібоначчієві числа, завадостійкість, надійність.

#### СПИСОК ЛИТЕРАТУРЫ

- 1. Обнаружение и исправление ошибок в дискретных устройствах / В. С. Толстяков, В. Н. Номоконов, М. Г. Карповский, И. Л. Ерош. М.: Сов. радио, 1972. 288 с.

- 2. Савченко Ю. Г. Цифровые устройства, нечувствительные к неисправностям элементов / Ю. Г. Савченко. М.: Сов. радио, 1977. 173 с.

- 3. Основы надежности цифровых устройств : учеб. пособие / В. С. Харченко, Жихарев В. Я., Илюшко В. М. и др. Харьков : Нац. аэрокосм. ун-т. «Харк. авиац. ин-т», 2004. 573 с.

- 4. Оберман Р. М. М. Счет и счетчки / Р. М. М. Оберман. М. : Радио и связь, 1984. 176 с

- Березюк Н. Т. Кодирование информации / Н. Т Березюк, А. Г. Андрущенко, С. С. Мощинський. – Харьков : Высшая школа, 1978. – 252 с.

- 6. Борисенко А. А. Методы синтеза информационных систем на основе позиционных чисел с неоднородной структурой: дис.... д-ра техн. наук: 61:895/922-6 / А. А. Борисенко. Харьков: 1991.

- 7. Стахов А. П. Основы математики гармонии и ее приложения / А. П. Стахов. М. : Академия Тринитаризма, 2013. Ч. 2. 318 с.

- 8. Щербаков Н. С. Самокорректирующие дискретные устройства / Н. С. Щербаков. М. : Машиностроение, 1975. 215 с.

- 9. Куно  $\Gamma$ . В. Разработка специализированных цифровых устройств с повышенной достоверностью функционирования на основе двоичных биполярных счетчиков дис. ... канд. техн. наук: 61:895/922-6 /  $\Gamma$ . В. Куно. Харьков: 1988. 217c.

- 10. Хетагуров Я. А. Повышение надежности цифровых устройств методами избыточного кодирования / Я. А.Хетагуров, Ю. П. Руднев. М.: Энергия, 1974. 376 с.

- 11. Павлов А. А. Метод построения отказоустойчивых дискретных устройств на основе корректирующих кодов повышенной обнаруживающей способности / А. А. Павлов, А. Н. Кузнецов // КомпьюЛог. 1998. 4(28). 49-51 с.

- 12. Ворисенко А. А. Биномиальные автоматы / А. А. Борисенко. Сумы : Изд-во СумГу, 2005. 121 с.

- 13. Стахов А. П. Коды золотой пропорции / А. П. Стахов. М. : Радио и связь, 1984. 152 с.

- 14. Об одном способе построения счетчиков Фибоначчи / А. А. Борисенко, А. П. Стахов, С. М. Маценко, В. В. Сиряченко // В сник Сумського державного ун верситету. Сер я Техн чн науки. 2012. Ч. 3. С. 165-170.

Поступила в редакцию 29 октября 2013 г.