УДК 519.873

# Г. Кривуля, Е. Сыревич, И. Власов,О. Павлов ОСОБЕННОСТИ ПРИМЕНЕНИЯ НАНОМЕМРИСТОРНОЙ ЛОГИКИ ДЛЯ ПРОЕКТИРОВАНИЯ ЦИФРОВЫХ СИСТЕМ

**Введение.** Развитие наноэлектроники позволило осуществить практическую реализацию четвертого базового элемента схемотехники — мемристора, который является дополнением к резистору, конденсатору и индуктивности. Мемристор (memory resistor) представляет собой двухполюсник с нелинейной вольтамперной характеристикой, обладающий гистерезисом — он способен запоминать свое сопротивление, которое зависит от последней величины приложенного к нему напряжения. [1].

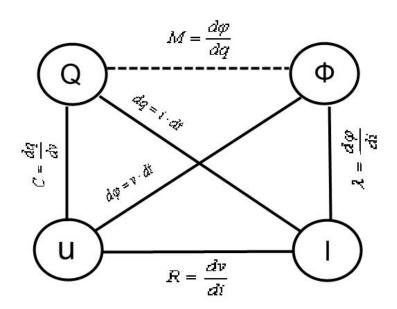

Взаимную зависимость четырех фундаментальных электрических величин – заряда (Q), напряжения (U), магнитного потока ( $\Phi$ ) и электрического тока (I) можно представить в виде полного графа с четырьмя узлами и шестью связями между ними (рис.1).

Рис.1. Взаимосвязь фундаментальных электрических величин

Связи между электрическими величинами обеспечиваются традиционными элементами (сопротивлением  $\mathbf{R}$ , индуктивностью  $\mathbf{L}$ , ёмкостью  $\mathbf{C}$ ) и мемристором  $\mathbf{M}$ . При этом на резисторе происходит падение напряжения при прохождении тока, емкость конденсатора связывает заряд на его обкладках и напряжение между ними, а индуктивность определяет соотношение между изменениями силы электрического тока и магнитного потока. Диагонали квадрата представляют собой уравнения, связывающие заряд с током и магнитный поток с напряжением.

Верхняя сторона квадрата, связывающая заряд с магнитным потоком, была реализована только после появления мемристора. Если воспользоваться соотношениями  $d\phi = v \cdot dt$  и  $dq = i \cdot dt$ , то можно записать связь между током и напряжением на мемристоре как:  $v = i \cdot M(q)$ . Очевидно, что в случае M=const мемристор представляет собой обычное сопротивление и полученное уравнение превращается в закон Ома для участка электрической цепи.

Электрическое сопротивление мемристора зависит от полярности прилагаемого напряжения и зависимости от знака разности потенциалов мемристор может находиться в выключенном (менее проводящем) состоянии и во включенном (более проводящем). В таком виде он мало отличается от диода. Главным качеством мемристора является зависимость его сопротивления от заряда в пределах от долей ома до сотен ом.

Свойства мемристора дают возможность применять его сразу в нескольких вариантах: переключателя, элемента памяти и составляющей логического элемента. При использовании мемристора в качестве биполярного переключателя: при подаче напряжения противоположной полярности мемристор замыкает или размыкает проходящую через него цепь. С точки зрения цифровой электроники мемристор переходит из состояния «0» в состояние «1» и наоборот. Причем это состояние мемристор «запоминает» и может хранить практически неограниченно долго без источника напряжения на его входах.

**Целью настоящей работы** является рассмотрение возможности применения мемристоров в качестве альтернативы существующих базовых элементов для логического проектирования цифровых систем.

Для дальнейшего рассмотрения поставленной задачи примем следующие ограничения: – мемристор существует и обладает высокой надежностью; – физические особенности мемристора существенно влияют на реализуемую логическую функцию.

Будем оперировать понятием **мемвентиль** (по аналогии с логическим вентилем). Полностью абстрагироваться от физической составляющей мемристора невозможно, т.к. по своим свойствам один мемристор практически бесполезен – необходимо рассматривать взаимное влияние мемристоров, способы подключения серии мемристоров, направление тока и т.д. Следует отметить, что вместо обособленно включенного мемристора рассматривают так называемые кроссбары (*crossbar*). Кроссбар или кроссбарная система – это слои мемристоров, уложенные перпендикулярно друг к другу, то есть фактически система с координатными переключателями [2].

## 1. Мемристорный логический элемент для реализации импликации.

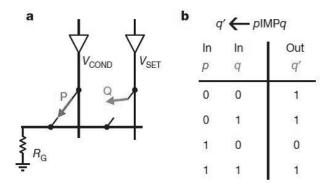

В [2] показано, что параллельное подключение двух мемристоров реализует функцию материальной импликации (material implication) На рис.2 показано вертикально-параллельное подключение двух мемристорных переключателей Р и Q к горизонтальной общей «земле» через нагрузочный резистор (рис. 2a) и таблица истинности функции импликации (рис.2б).

Рис.2а-2б. Мемристоры и табл. истинности

Переменные р и q соответствуют выходным состояниями переключателей. Вертикальные линии содержат тристабильный буфер (если он находится в пассивном состоянии, то его выход принимает высокоимпедансное состояние). Каждый переключатель можно перевести в закрытое состояние (логическая 1) отрицательным напряжением VSET, поданным на его тристабильный буфер. Для компенсации падения напряжения на нагрузочном резисторе, значение VSET должно быть несколько больше VCLOSE. Аналогично, для получения логического 0 нужно приложить положительное напряжение VCLEAR, превышающее VOPEN. Т Установка логической 1 на мемристоре означает получение низкоимпедансного состояния на его выходе, а сброс в 0 – высокоимпедансного состояния. Отрицательное напряжение VCOND, которое несколько меньше VSET, не изменяет состояние ведомого устройства; его значение будет показано ниже.

Главным в импликативной операции является то, что вычисления выполняются при определенных условиях переключения мемристоров. Синхронизированное вычисление импликация выполняется путем одновременного приложения импульса с амплитудой  $V_{\text{SET}}$  к Q и импульса с амплитудой VCOND к P. Если отдельно приложить  $V_{\text{SET}}$  к Q , то q'=1, если  $V_{\text{COND}}$  к P, то p'=p. Если эти напряжения приложены одновременно, то они вызывают изменения, зависящие от исходных состояний двух мемристоров. Если P был открыт (p=0), то Q оказывается закрытым, независимо от своего исходного состояния (q'=1), а состояние P не меняется (p'=p). Если же P закрыт (p=1), то импульс  $V_{\text{COND}}$  уменьшает напряжение на Q, и оба мемристора P и Q остаются в неизменном состоянии (p'=p, q'=q). Для выполнения операция импликация переключатели надо подготовить, т.е. установить соответствующие начальные p и q.

Предложенная реализация предполагает формирование элемента, аналогичного, с одной стороны, логическому элементу, а с другой — триггеру-«защелке». Такой «мемвентиль» использует сопротивление вместо напряжения или заряда в качестве переменной, описывающей физическое состояние.

Наряду с универсальными элементами И-НЕ и ИЛИ-НЕ функция импликации, совместно с функцией константа ноль, формирует функционально полный базис, то есть на ее основе можно выполнить все 16 переключательных функций двух переменных (рис. 3)

| X  | 0                   | 0 | 1 | 1                                   | Heverille in out the operation (V, V)                                 |                                                                               |  |  |

|----|---------------------|---|---|-------------------------------------|-----------------------------------------------------------------------|-------------------------------------------------------------------------------|--|--|

| Y  | 0 1 0               |   | 1 | Исходные двоичные аргументы (Х , Ү) |                                                                       |                                                                               |  |  |

| №  | Значение<br>функции |   |   |                                     | Название функции F <sub>i</sub> = (x.y)                               | <b>F</b> <sub>i</sub> в базисе <b>F</b> <sub>0</sub> , <b>F</b> <sub>13</sub> |  |  |

| 0  | 0                   | 0 | 0 | 0                                   | константа 0 $F_0 = 0$                                                 | 0                                                                             |  |  |

| 1  | 0                   | 0 | 0 | 1                                   | коньюнкция $F_1 = X \Lambda Y$                                        | (X⇒(Y⇒0))⇒0                                                                   |  |  |

| 2  | 0                   | 0 | 1 | 0                                   | отрицание импликации $X \Rightarrow Y$ $F_2 = \neg (X \Rightarrow Y)$ | (X⇒Y)⇒0                                                                       |  |  |

| 3  | 0                   | 0 | 1 | 1                                   | переменная $X 	 F_3 = X$                                              | (X⇒0) ⇒0                                                                      |  |  |

| 4  | 0                   | 1 | 0 | 0                                   | отрицание импликации $Y \Rightarrow X$ $F_4 = \neg (Y \Rightarrow X)$ | (X⇒ Y)⇒0                                                                      |  |  |

| 5  | 0                   | 1 | 0 | 1                                   | переменная $Y 	 F_5 = Y$                                              | (Y⇒0)⇒0                                                                       |  |  |

| 6  | 0                   | 1 | 1 | 0                                   | отрицание эквивалентности $F_6 = \neg (X \Leftrightarrow Y)$          | $(X\Rightarrow Y)\Rightarrow ((Y\Rightarrow X)\Rightarrow 0)$                 |  |  |

| 7  | 0                   | 1 | 1 | 1                                   | дизьюнкция $F_7 = X V Y$                                              | $(X\Rightarrow Y)\Rightarrow (Y\Rightarrow X))\Rightarrow 0$                  |  |  |

| 8  | 1                   | 0 | 0 | 0                                   | отрицание дизьюнкции $F_8 = \neg (X \ V \ Y)$                         | $((X \Rightarrow 0) \Rightarrow Y) \Rightarrow 0$                             |  |  |

| 9  | 1                   | 0 | 0 | 1                                   | эквивалентность F <sub>9</sub> = X ⇔ Y                                | $(X\Rightarrow Y)\Rightarrow ((Y\Rightarrow X)\Rightarrow 0))\Rightarrow 0$   |  |  |

| 10 | 1                   | 0 | 1 | 0                                   | отрицание Y $F_{10} = \neg Y$                                         | Y⇒0                                                                           |  |  |

| 11 | 1                   | 0 | 1 | 1                                   | импликация $YX$ $F_{11} = Y \Rightarrow X$                            | $Y \Rightarrow X$                                                             |  |  |

| 12 | 1                   | 1 | 0 | 0                                   | отрицание X $F_{12} = \neg X$                                         | X⇒0                                                                           |  |  |

| 13 | 1                   | 1 | 0 | 1                                   | импликация $XY$ $F_{13} = X \Rightarrow Y$                            | $X \Rightarrow Y$                                                             |  |  |

| 14 | 1                   | 1 | 1 | 0                                   | отрицание конъюнкции $F_{14} = \neg (X \ \Lambda \ Y)$                | $X \Rightarrow (Y \Rightarrow 0)$                                             |  |  |

| 15 | 1                   | 1 | 1 | 1                                   | константа 1                                                           | X⇒X                                                                           |  |  |

Рис. 3. Реализация логических функций двух переменных на основе импликативного базиса

# 2. Реализации универсального логического элемента на основе трех мемристоров

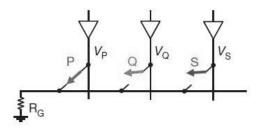

Существует возможность реализации универсального логического элемента И-НЕ (s=p and q) на основе трех мемристоров, включенных вертикально-параллельно на общую горизонтальную шину (рис.4).

Рис. 4. Вертикально-параллельное подключение трёх мемристорных переключателей P, Q, S к горизонтальной общей «земле» через нагрузочные резисторы

Подготовка переключателей проходит в два этапа: установка мемристора s в 0, формирование нового значения на s через функцию импликации между первым и вторым переключателями s'=s $\rightarrow$ p, затем заключительный шаг – вычисление И-НЕ (NAND) через импликацию s''=s' $\rightarrow$ q (Рис. 5).

| шаг 1 | шаг 2 |   |    | шаг 3 |    |    |

|-------|-------|---|----|-------|----|----|

| S     | p     | s | s' | q     | s' | s" |

| 0     | 0     | 0 | 1  | 0     | 1  | 1  |

| 0     | 0     | 0 | 1  | 1     | 1  | 1  |

| 0     | 1     | 0 | 0  | 0     | 0  | 1  |

| 0     | 1     | 0 | 0  | 1     | 0  | 0  |

Рис. 5. Последовательность подачи уровней напряжений для вычисления функции NAND

### 3. Реализации инвертора на мемристорах

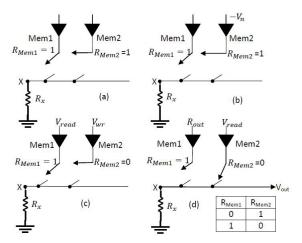

Еще один элемент, который можно реализовать на мемристорах, — это инвертор. Для этого потребуется два мемристора, включенных аналогично мемвентилю, реализующему функцию импликации. Мемристор Mem1 — управляющий и его состояние не меняется. Состояние мемристора Mem2 изменяется в соответствие с функцией отрицания НЕ. Вычисление значения проходит в три этапа. На первом этапе (безусловно—разомкнутое состояние) Mem2 устанавливается в разомкнутое состояние путем подачи высокого импеданса на вход — мемристор Mem1 и отрицательного напряжения на вход Mem2. Напряжение — больше, чем порог для размыкания мемристора, и поэтому состояние Mem2 устанавливается в лог. 1 независимо от предыдущего состояния.

На рис.6 пнедставлено вертикально-параллельное подключение двух мемристорных переключателей Mem1 и Mem2 к горизонтальной общей «земле» через нагрузочный резистор и последовательность подачи управляющих напряжений

Рис. 6. Реализация инвертора на мемристорах

Аналогично классическому представлению цифровой логики в формулировке Шеннона физическим эквивалентом или логическим состоянием мемристорного импликативного элемента будет величина сопротивления на переключателе, что и добавляет этому элементу характеристику «запоминания».

# 4. Последовательностные устройства на мемристорах

Аналогично классическому представлению цифровой логики в формулировке Шеннона физическим эквивалентом или логическим состоянием мемристорного импликативного элемента будет величина сопротивления на переключателе, что и добавляет этому элементу характеристику «запоминания».

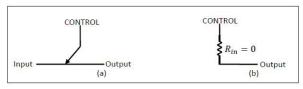

Рассмотрим реализацию простейшего триггера на основе двух мемристоров. Начнем с реализации простого двухпозиционного переключателя. Один из выводов мемристора подсоединен к источнику управляющих значений (управляющих напряжений), а другой – либо к входу, либо к выходу (рис.7).

Рис. 7. Переключатель с функцией запоминания

Когда мемристор закрыт, на нем – нулевое сопротивление между управляющей и входной линиями, то есть лог. 0. Лог.0 может быть считан при подачи положительного напряжения на управляющий вывод.

Затем напряжение считывается с выхода. Высокое напряжение указывает на лог. 0, т.к. сопротивление равно нулю.

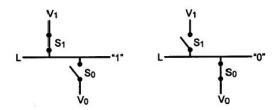

Для полноценной замены полупроводниковых устройств другими приборами необходимо реализовать простейшую функцию хранения значений в дополнение к возможности эти значения вычислять. Пусть «сигнальная» линия L может быть установлена в лог. 1 или лог. 0 двумя переключателями с памятью  $S_0$  и  $S_1$  (они соответствуют двум мемристорам). Переключатель  $S_0$  соединяет L с источником напряжения  $V_0$ , который подтягивает к нулю, тогда как  $S_1$ , соединенный с источником  $V_1$ , подтягивает к единице. Если  $S_0$  ( $S_1$ ) замкнут, а  $S_1$  ( $S_0$ ) — разомкнут, то на линии L будет лог. 0 (1) в вольтовой интерпретации. Таким образом, значение на переключателях (это мемристоры, у которых логические значения вычисляются по величине сопротивления) может быть получено в вольтовом эквиваленте,  $V_0$  ог  $V_1$ , на линии L. Как только переключатели установлены, можно получить инверсное значение путем обмена источников напряжения. На рис.8 показано встречно-параллельное подключение двух мемристорных переключателей  $S_1$  и  $S_2$  к общей «сигнальной» линии

Рис. 8. Реализация функции запоминания

Элемент-защелка также должна преобразовывать входное логическое значение на линии L (в вольтах) в эквивалентную конфигурацию переключателей  $S_0$  и  $S_1$  (память), что требует способность переключать  $S_0$  и  $S_1$  соответствующими управляющими напряжениями. Это такая же необходимая операция, как и установка бита в памяти из массива двухпозиционных переключателей, соединенных по принципу металмолекула-метал.

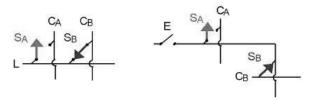

Стандартные полупроводниковые тригтеры-защелки используют для переключения транзисторы с тремя выводами. Ниже описана концепция элемента-защелки, которую далее можно реализовать на двухвыводном устройстве на кроссбаре (взаимоперпендикулярных слоях мемристоров). На рис.9 приведено встречно-параллельное подключение двух мемристорных переключателей SA и SB к общей «сигнальной» линии

Рис. 9 .Триггер – защелка.

Две управляющие линии  $C_A$  и  $C_B$  связаны «сигнальной» линией L с двухпозиционными двухвыводными переключателями  $S_A$  и  $S_B$ . Переключатели обладают индивидуальной полярностью и пороговым напряжением для переключения между закрытым и открытым состоянием. Переключатели по своей полярности ориентированы встречно-параллельно (показано стрелками). Линия сигнала имеет, как минимум, два состояния (уровня напряжения) в диапазоне от лог. 0 до лог. 1. Если источником входного значения вход на линии является выход диода/резистора, то величина напряжения будет ниже истинного 0 или 1. Важнейшая функция защелки состоит в том, чтобы восстановить это значение до приемлемого. Для выполнения полной операции «защелкивания», подается последовательность импульсов напряжения на каждый управляющий переключатель, которая, сначала, безусловно их открывает, потом условно закрывает один из них, а затем восстанавливает (или инвертирует) значение на линии L.

ВАХ двух молекулярных двустабильных переключателей ( $S_A$  и  $S_B$ ) имеет гистерезис в форме восьмерки. Полярность напряжения определяется положительным или передним приращением по току, проходящему через переключатель в направлении стрелки. При небольших значениях напряжения 0,7 В переключатели ведут себя, как стабильные нелинейные резисторы и в открытом, и в закрытом состоянии. Переключение достигается при приложении смещения, превышающего положительный или отрицательный порог для открытия или закрытия переключателя.

Триггер состоит из двух переключателей, и расхождения их ВАХ объясняется назначенными диапазонами открывающего и закрывающего напряжения. Напряжение, превышающее максимальное в диапазоне «открытого» («закрытого») состояния закрывает (открывает) любой переключатель.

Относительная последовательность диапазонов, соответствующих открытому/закрытому состоянию и состоянию лог. 1/0 «защелкивают» значения функции, но величина напряжений зависит от определения потенциала земли.

Таким образом, доступно 4 переключательные операции путем изменения напряжений на управляющей линии любого переключателя.

Под сигнальной линией понимают линию, принимающую уровень напряжения между сильным 0 и сильной 1. Наведение (индукция) большого обратного смещения безусловно откроет переключатель независимо от напряжения на сигнальной линии. Аналогично большое прямое смещение безусловно закроет переключатель. Открытие и закрытие переключателя типа «метал-молекула-метал» при условии такой безусловной операции — стандартная операция для установки и сброса бит в памяти и для задания программируемых логических функций.

Возможность создания условных импульсов на открытие и закрытие переключателя отличает рассматриваемый вариант двустабильного переключателя от традиционных. Если напряжение на сигнальной линии находится между слабой 0 и сильной 0, то прикладывая условный импульс на открытие к управляющей линии, можно открыть переключатель. Однако если напряжение на сигнальной линии находится между сильной 1 и слабой 1, то тот же условный импульс на открытие, приложенный к управляющей линии, не откроет переключатель, т.к. потенциал на переходе не достигнет порогового. И наоборот, условный импульс на закрытие может закрыть переключатель, если только напряжение на сигнальной линии будет, по крайней мере, равен слабой 1.

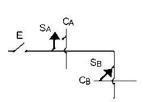

Ниже приведен пример подключения мемристоров с совпадением полярности. Такое однонаправленное подключение не создает возможностей для условного переключения между 0 и 1 (рис.10).

Рис. 10. Однонаправленное подключение двух мемристорных переключателей  $S_{_{\rm A}}$  и  $S_{_{\rm B}}$

Рассмотрим пример. Оба переключателя можно безусловно открыть, но только лог. 1 можно использовать для условного закрытия переключателя и хранения 1. Соответственно, оба переключателя можно безусловно установить в 0, но только лог. 0 может быть впоследствии условно сохранен. Разворачивание полярности переключателя  $S_{\rm B}$  убирает это ограничение; теперь возможна операция условного закрытия переключателя и при входной лог. 1 и при 0. Теперь операция «защелкивания» выполняется в три этапа:

- 1. Безусловно открыть оба переключателя  $S_A$  и  $S_B$  подачей импульса надпорогового напряжения с положительным смещением на  $C_A$ , а с отрицательным на  $C_B$ .

- 2. Подать условные закрывающие импульсы на обе управляющие линии (отрицательные на  $C_{\rm A}$  и положительные на  $C_{\rm B}$ ).

- 3. Подать сильную 1 на линию  $C_A$  сильный 0 на  $C_B$  для восстановления полного значения на линии L. Если исходное значение напряжения на этой линии было между слабой 1 и сильной 1, то шаги (i) и (ii) закроют переключатель  $S_A$  и оставят  $S_B$  в открытом состоянии. Тогда как если начальное значение было между слабым и сильным нулем, то  $S_A$  будет открыт, а  $S_B$  закрыт. Шаг (ii) можно выполнить одновременно для обоих переключателей или последовательно один за другим. Если входное напряжение на линии сигнала уменьшено из-за шума, потерь на сопротивлении или падения на диодах, то напряжение восстановится до полного уровня. «Защелка» обеспечивает выполнение операции логической инверсии. На последнем шаге (iii) после запоминания сигнала, его необходимо отключить от входа и изменить полярность напряжения на  $C_A$  и  $C_B$ .

**Выводы.** Мемристор можно рассматривать как универсальный элемент, который позволяет реализовать как логические стандартные функции, так и функции запоминания, образуя полную функциональную систему для логического проектирования цифровых систем.

Недостаток мемристорной логики заключается в том, что физическая реализация импликативного элемента осуществлена только в виде соединения двух мемристоров. Кроме того, необходимо разработать

методы адаптации известных методов проектирования цифровых устройств к новой элементной базе. Очевидно, что существует ряд проблем, которые могут возникнуть при внедрении новой элементной базы, так как взаимовлияние мемристоров не полностью изучено и требуются примеры реализации схемы синхронизации на мемристорах

### ЛИТЕРАТУРА

- 1. Chua L.O. Memristor the missing circuit element. IEEE Trans. Circuit Theory, 1971, v.18, p.507–519.

- 2. Strukov D.B., Snider G.S., Stewart D.R., Williams R. S. The missing memristor found. Nature letters, 2008, v.453, p.80–83.

- 3. Kuekes P.J., Stewart D.R., Williams R.S. The crossbar latch: Logic value storage, restoration, and inversion in crossbar circuits // American Institute of Physics, Journal of Applied Physics, 2005

- 4. Ketaki Kerur B.E. A Study of The Memristor, The Fourth Circuit Element // Visvesvaraya Technological University, 2007

- 5. Елисеев Н. Мемристоры и кроссбары: нанотехнологии для процессоров // ЭЛЕКТРОНИКА: Наука, Технология, Бизнес. 2010. С. 84-89

- 6. Borghetti J., Snider G.S., Kuekes P.J. et al. 'Memristive' switches enable 'stateful' logic operations via material implication. Nature letters, 2010, v.464, p.873–876

- 7. Tezaswi R., Samiha M. Digital Logic Implementation in Memristor-Based Crossbars // A Tutorial, 5th IEEE International Symposium on Electronic Design, Test & Applications, 2010.

- 8. Кривуля Г.Ф., О.А. Павлов, И.В. Власов . Четвертый базовый элемент схемотехники мемристор основа будущих интеллектуальных систем. Материалы международной конференции «Интеллектуальные системы принятия решений » ISDVCI-2012 . Евпатория , 27-31.05.2012 Стр.110-1

- 9. Кривуля Г.Ф., О.А. Павлов, И.В. Власов. Применение мемристорной логики в компьютерной инженерии. Інформаційно керуючі системи на залізничному транспорті. 2012.–№4. с.3-7.