## Electrical Properties of High-k Oxide in Pd/Al<sub>2</sub>O<sub>3</sub>/InGaAs Stack

Y.Y. Gomeniuk<sup>1,\*</sup>, A.N. Nazarov<sup>1</sup>, S. Monaghan<sup>2</sup>, K. Cherkaoui<sup>2</sup>, E. O'Connor<sup>2</sup>, I. Povey<sup>2</sup>, V. Djara<sup>2</sup>, P.K. Hurley<sup>2</sup>

Lashkaryov Institute of Semiconductor Physics, NAS of Ukraine, 41, pr. Nauki, 03028 Kyiv, Ukraine

Tyndall National Institute, University College Cork, Lee Maltings, Prospect Row, Cork, Ireland

(Received 23 June 2012; published online 13 August 2012)

The paper presents the results of capacitance-voltage (C-V) characterization of metal-oxide-semiconductor (MOS) structure, namely  $Pd/Al_2O_3/In_{0.53}Ga_{0.47}As/InP$ . It is shown that MOS structure under study exhibit both electron and hole trapping with permanent and temporary charge trapping contributions. The interfacial transition layer between the high-k oxide and InGaAs has the greatest influence on this charge trapping phenomenon.

Keywords: High-k oxide, InGaAs, MOS structure, MOSFET, C-V, ALD, Interface states.

PACS numbers: 72.20.Jv, 73.20. - r, 73.40.Qv

#### 1. INTRODUCTION

Searching for ultrathin gate dielectric materials is one of the major challenges associated with further downscaling in CMOS technology. High dielectric constant (high- $\kappa$ ) materials with higher permittivity than SiO<sub>2</sub> can be grown thicker providing the same equivalent oxide thickness (EOT) and significant decreasing of gate leakage currents.

While high speed logic and RF applications require implementing of high mobility channel materials such as Ge or InGaAs into CMOS technology the use of high-  $\kappa$  dielectric materials in conjunction with III-V substrate is highly required for the demands of future progress and improvement of MOSFET performance.

It has been reported [1, 2] that high-κ materials often suffer from the charge trapping and poor electrical quality of the dielectric-semiconductor interface as compared to SiO<sub>2</sub>. In addition the high-κ/InGaAs MOS system exhibits a relatively high level of interface states (D<sub>it</sub>) and fixed oxide charges (QF) [3, 4], both of which induce threshold voltage shifts and degrade carrier mobility in InGaAs MOSFETs. The understanding of interface (D<sub>it</sub>) and bulk defects in the high-κ/In<sub>x</sub>Ga<sub>1-x</sub>As/InP metaloxide-semiconductor (MOS) system will be essential for the successful implementation of high mobility channel materials in MOS Field Effect Transistor (MOSFET).

In this work we present results of a study focused on the characterization of interface defects and bulk electron/hole traps in the high- $\kappa/In_{0.53}Ga_{0.47}As/InP$  MOS system.

## 2. EXPERIMENTAL

The studies were performed on Pd/Al $_2$ O $_3$ / In $_{0.53}$ Ga $_{0.47}$ As/InP MOS structures with high- $\kappa$  Al $_2$ O $_3$  oxide layers formed by atomic layer deposition (ALD) of nominal physical thickness of 5, 10, 15 and 20 nm. The top Pd gate metallization was obtained by a shadow mask process. The samples received no postmetallization annealing treatment. To investigate hole and electron trapping in the bulk of oxide film, samples with both n- and p- type doped (4  $\times$  10 $^{17}$  cm $^{-3}$ ) In $_{0.53}$ Ga $_{0.47}$ As epitaxial layers were examined.

MOS capacitors were characterized by capacitancevoltage (C-V) measurements at room temperature using an Agilent E4980A Precision LCR meter.

# 3. RESULTS AND DISCUSSION

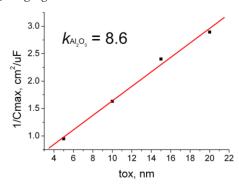

Fig. 1 presents the relation between inverse of maximum accumulation capacitance,  $1/C_{\rm max},$  and oxide thickness, tox, for  $Al_2O_3/In_{0.53}Ga_{0.47}As$  MOS structure with  $t_{\rm OX}$  ranging from 5 nm to 20 nm.

Fig.  $1-1/C_{\rm max}$  versus oxide thickness (tox) for MOS structures with tox ranging from 5 nm to 20 nm

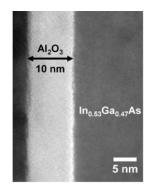

The  $Al_2O_3$   $\kappa$ -value (8.6) was obtained from the slope of the capacitance equivalent thickness in accumulation versus the oxide thickness  $t_{ox}$ . The cross-sectional high resolution transmission electron microscopy (HRTEM) image through the gate oxide region confirmed a nominal thickness of 10 nm (Fig. 2).

The high- $\kappa/In_{0.53}Ga_{0.47}As$  system typically exhibit interface state densities  $(D_{it})$  to be in the range mid- $10^{12}$  to  $10^{13}$  cm<sup>-2</sup> eV<sup>-1</sup> [4-6]. Analysis of the capacitance-voltage (C-V) response indicates interface states of predominantly donor type with  $D_{it}$  ranging from  $0.8 \times 10^{13}$  to  $1.5 \times 10^{13}$  cm<sup>-2</sup>. These results are consistent with  $As_{Ga}$  antisite defects based on hybrid density functional calculations of point defects in III–V compounds [7]. Recent studies show that similar C-V responses are obtained for a wide range of oxides ( $SrTa_2O_6$ ,  $HfO_2$ ,  $Si_3N_4$ ) which could be the result of the defects originating from  $In_{0.53}Ga_{0.47}As$  surface.

<sup>\*</sup> ygomeniuk@gmail.com

**Fig. 2** – Cross sectional HRTEM image of the structure with  $t_{OX} = 10$  nm.

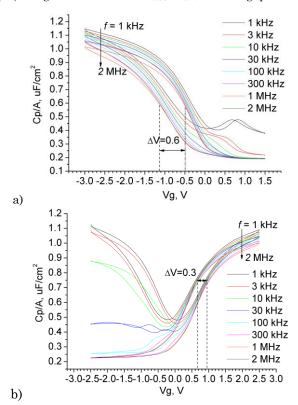

High-frequency C-V characteristics were measured on MOS capacitors at room temperature (Fig. 3). The results indicate that both electrons and holes are trapped for n- and p-  ${\rm In}_{0.53}{\rm Ga}_{0.47}{\rm As}$  MOS structures, respectively. The flatband voltage shift corresponds to charge trapping (Q<sub>T</sub>) level of  ${\sim}1{\rm x}10^{13}$  cm- $^2$  which is comparable to, or larger than, the interface state density (D<sub>it</sub>) integrated across the  ${\rm In}_{0.53}{\rm Ga}_{0.47}{\rm As}$  band gap.

Fig. 3 – Frequency dependence of C-V characteristic for a Pd/Al $_2$ O $_3$ (5nm)/p- (a) n- (b) In $_{0.53}$ Ga $_{0.47}$ As/InP MOS structure at room temperature.

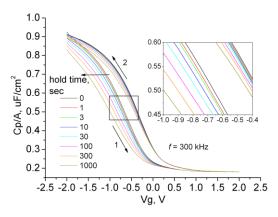

Moreover, the trapping is primarily a reversible process, where the trapped charge removed at the onset of a second C-V hysteresis sweep. More C-V sweeps were carried out with charging in accumulation regime within hold time of 1, 3, 10, 30, 100, 300 and 1000 seconds which showed no presence of degradation after tests (Fig. 4).

**Fig. 4** – High-frequency (300 kHz) C-V characteristics biased at accumulation regime within hold time of 1, 3, 10, 30, 100, 300 and 1000 seconds at room temperature.

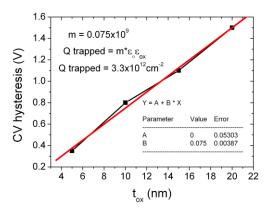

The trapped charge density also depends on the hold time and maximum gate bias. Based on samples with variable high- $\kappa$  thickness, C-V hysteresis studies reveal a linear increase in C-V hysteresis with increasing oxide thickness (Fig 5). All of these experimental observations and analysis are consistent with the charge trapping taking place primarily as a line charge at the high- $\kappa/In_{0.53}Ga_{0.47}As$  interface, which can contain native oxides of Ga, In and As [8].

**Fig. 5** – C-V hysteresis as a function of oxide thickness for Pd/Al<sub>2</sub>O<sub>3</sub>/n-In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS structure. The linear increase in C-V hysteresis (or  $\Delta$ V) with increasing oxide thickness indicates the trapping charge is primarily a sheet charge,  $\Delta$ V =  $Q_{trapped}$  \* ( $t_{co}/\epsilon_0\epsilon_{ox}$ ). From the gradient  $Q_{trapped}$  = 3.3 x  $10^{12}$  cm<sup>-2</sup> (negative charge).

In summary, Pd/high- $\kappa$ /In<sub>0.53</sub>Ga<sub>0.47</sub>As/InP MOS capacitors exhibit both electron and hole trapping with permanent and temporary charge trapping contributions. The interfacial transition layer between the high- $\kappa$  oxide and In<sub>0.53</sub>Ga<sub>0.47</sub>As has the greatest influence on this charge trapping phenomenon.

### AKNOWLEDGEMENTS

The authors would like to thank Science Foundation Ireland for financial support of the project (09/IN.1/I2633, the INVENT project). This work has been partly funded by the National Academy of Sciences of Ukraine in frames of the Complex Program of Fundamental Research "Nanosystems, nanomaterials and nanotechnologies", project No. 53/32/12-H.

### REFERENCES

- 1. H. Wong, H. Iwai, Microelectron, Eng. 83, 1867 (2006).

- O. Engström, B. Raessi, S. Hall, O. Buiu, M.C. Lemme, H.D.B. Gottlob, P.K. Hurley, K. Cherkaoui, Solid-State Electron. 51, 622 (2007).

- 3. G. Brammertz, et al., Appl. Phys. Lett. 95, 202109 (2009).

- É. O'Connor, S. Monaghan, R. D. Long, A. O'Mahony, I. M. Povey, K. Cherkaoui, M. E. Pemble, G. Brammertz, M. Heyns, S.B. Newcomb, V.V. Afanas'ev, P.K. Hurley, Appl. Phys. Lett. 94, 102902 (2009).

- G. Brammertz, H. C. Lin, K. Martens, et al. *J. Electro-chem. Soc.* 155, H945 (2008).

- Yoontae Hwang, Roman Engel-Herbert, Nicholas G. Rudawski, and Susanne Stemmer, Appl. Phys. Lett. 96, 102910 (2010).

- 7. H-P Komsa, A. Pasquarello, *Microelectron. Eng.* **88**, 1436 (2011).

- 8. R.D. Long, et. al., J. Appl. Phys. 106, 084508 (2009).